# **Reed Solomon Codec (Errors-only)**

## **CMS0007**

- Errors Only Reed-Solomon CODEC using the Berlekamp Massey algorithm for efficient implementation.

- Register programmable, fixed or synchronous "onthe-fly" loading for different values of N in a Reed-Solomon (N, N-2T) code. T fixed by synthesis.

- Supports shortened codes.

- Can be synthesised for any Galois Field, Reed-Solomon code, and correcting power T, with maximum values for N set by synthesis parameters.

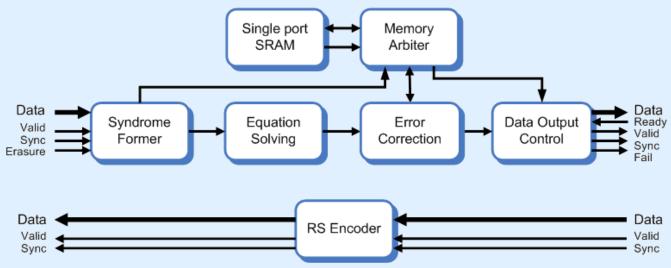

- Requires one single-port memory with storage for two non-shortened Reed Solomon blocks.

- Excellent performance in both FPGA and ASIC implementations.

#### **Contact information**

**Commsonic Ltd.** St. Johns Innovation Centre Cowley Road Cambridge CB4 0WS England

www.commsonic.com sales@commsonic.com tel. +44 1223 421845 fax +44 1223 421845

$\odot$  2007 Commsonic Ltd. All rights reserved. This information is subject to change without notice. 19 April, 2007 Revision 1.5

www.commsonic.com

**Block Diagram**

### **Detailed Description**

The Commsonic CMS0007 Reed Solomon Codec provides ultimate flexibility in its operation and build. The design uses the Berlekamp Massey algorithm in order to maximise speed and efficiency.

#### **Synthesis Parameters**

Setting up the Reed-Solomon codec is very simple. Firstly, it is necessary to set up the Galois field over which the code will operate using three parameters:

**gal\_bps.** Bits per symbol (typically 7 or 8 for communications applications).

gal\_alpha. Primitive root of the field (usually 2).

**gal\_field\_gen\_poly.** Field Generator Polynomial (e.g.  $x^8+x^4+x^3+x^2+1$  is usually used for GF{2<sup>8</sup>}.

Once the field is set up, the next task is to select the Reed-Solomon code parameters. This involves configuring the parameters:

**RS\_T.** The number of symbols that can be corrected per codeword.

**JO.** The first power of alpha used in the code generator polynomial.

The code polynomial G(x) is then determined by:

$$G(x) = (1 - \alpha^{J0}) (1 - \alpha^{J0+1}) \dots (1 - \alpha^{J0+2*RS_{T-1}})$$

These parameters are set once in a VHDL package and are applicable to the full design. The field and code parameters are set by constants and fixed for a particular implementation of the block.

#### **Register Configuration**

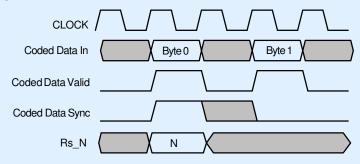

Once the code has been selected, it is possible to adapt the correcting power for a particular application by adjusting the values of N that is selectable using the register  $RS_N$ .

For example, if the code instantiation selected is an RS(255, 239) code then the decoder is capable of correcting eight errors in every 255 symbols - since N=255 and T=8 are the maximum values permitted by this instantiation. Setting RS\_N less than 255 will allow the same number of errors to be fixed in a shorter block size thereby increasing the correcting power of the code.

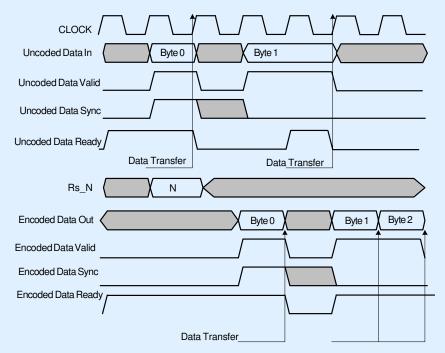

An additional feature is the ability to accept new value on N on a packet-by-packet basis. The value of N is loaded with sync and valid to allow *on-the-fly* changes. Alternatively the value of N may be tied to a constant to minimise gate count.

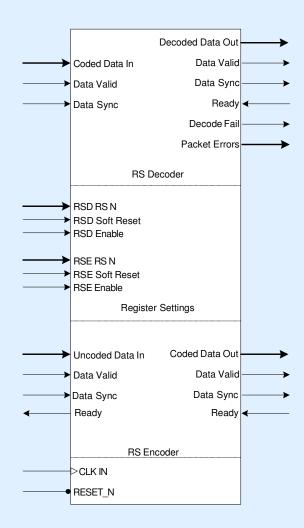

## **Principle I/O Description**

| Decoder I/O        |                                                                                 |

|--------------------|---------------------------------------------------------------------------------|

| Coded Data In      | Reed-Solomon encoded symbols                                                    |

| Coded Data Sync    | RS block start flag                                                             |

| Coded Data Valid   | Strobe signal for data and sync inputs                                          |

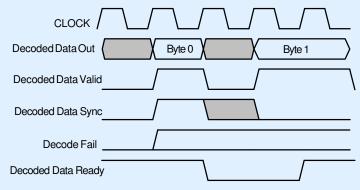

| Decoded Data Out   | The decoded and corrected data output symbols                                   |

| Decoded Data Sync  | Block start indicator for output blocks                                         |

| Decoded Data Valid | Strobe signal for output data and sync                                          |

| Decoded Data Ready | Device receiving data is ready. Data transfers when ready/valid are asserted    |

| Decode Fail        | Indicates that the block output decode failed due to too many errors.           |

| Packet Errors      | Number of errors fixed in the packet. Used in to construct a BER monitor.       |

| Encoder I/O        |                                                                                 |

| Uncoded Data In    | Non-coded data input symbols                                                    |

| Uncoded Data Sync  | Block start flag                                                                |

| Uncoded Data Valid | Strobe signal for data and sync inputs                                          |

| Uncoded Data Ready | Encoder ready for new data byte. Data transfers when ready/valid are asserted   |

| Coded Data Out     | The encoded data output symbols                                                 |

| Coded Data Sync    | Block start indicator for output blocks                                         |

| Coded Data Valid   | Strobe signal for output data and sync                                          |

| Coded Data Ready   | Interface ready for new data byte. Data transfers when ready/valid are asserted |

| Registers          |                                                                                 |

| RSD N              | The number of symbols in the encoded block. Stored at start of packet.          |

| RSD Soft Reset_N   | Soft reset for the RS Decoder.                                                  |

| RSD Enable         | Enable decoder. When clear data will be passed through without correction.      |

| RSE N              | The number of symbols in the encoded block. Stored at start of packet.          |

| RSE Enable         | Enable encoder. When clear data will be passed through without parity bytes.    |

| RSE Soft Reset_N   | Soft reset for the RS Encoder.                                                  |

| Others             |                                                                                 |

| clock              | Clock input.                                                                    |

| reset_n            | Asynchronous active-low reset input.                                            |

### **Timing Diagrams**

#### **RS Encoder packet start:**

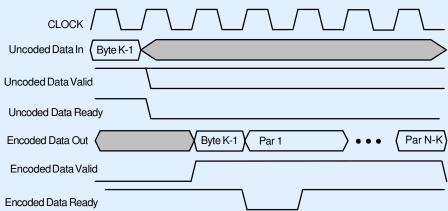

#### **RS Encoder packet end:**

### **Timing Diagrams (Cont'd)**

#### **RS Decoder Data Input:**

#### **RS Decoder Data Output:**

#### **EXAMPLE APPLICATION**

#### **DVB Decoder:**

A typical application for the RS Decoder is in a DVB decoder application. The field used is  $GF\{2^8\}$  generated with the polynomial  $x^8+x^4+x^3+x^2+1$ . The standard calls for an RS(204, 188) code which can be implemented by setting the value of RS\_N = 204 as a constant. The value of RS\_T is set as a synthesis parameter to 8.

#### **About Commsonic:**

Commsonic is an IP and design services company that specialises in the development of ASIC, FPGA, DSP and board-level sub-systems for applications in wireless and wireline communications.

Our expertise is primarily in the gate- and power-efficient implementation of physical-layer (PHY) functions such as modulation, demodulation and channel coding, but we have extensive experience with all of the major elements of a modern baseband 'core' including medium access control (MAC), voiceband DSP, mixed-signal interfaces and embedded CPU and software.

Our services are available on a turn-key basis but they are usually provided as part of a support package attached to members of our expanding family of licensable IP cores.

Commsonic's IP spans the major Standards for cable, satellite and terrestrial digital TV transmission and includes high-performance, adaptable, single-carrier (QAM) and multi-carrier (COFDM) modulator and demodulator solutions for DVB-S2, DVB-C/J.83/A/B/C and DVB-T/H.

Commsonic's customers are typically semiconductor vendors and manufacturers of broadband transceiver equipment that demand leading-edge Standards-based or proprietary PHY solutions but don't have the internal resources necessary to get their products to market soon enough.

**Commsonic Ltd.** St. Johns Innovation Centre Cowley Road Cambridge CB4 0WS England

www.commsonic.com sales@commsonic.com tel. +44 1223 421845 fax +44 1223 421845

© 2007 Commsonic Ltd. All rights reserved. This information is subject to change without notice.